XCEL ASICs

GmbH

Accelerator IP for WiGig (IEEE 802.11 AD) LDPC Decoder

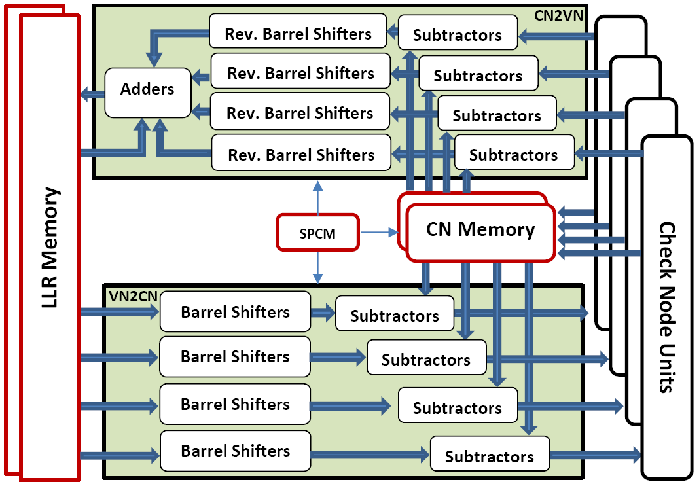

This IP core implements an optimized Low-Density Parity-Check (LDPC) decoder defined for the IEEE 802.11 ad (WiGig) standard. The core implements fast column message passing (FCMP) decoding which is the fastest-converging LDPC decoding reported so far. The faster convergence enables this implementation to achieve the best-reported energy-efficiency for a WiGig LDPC decoder.

The IP core:

-

implements FCMP decoding for the fastest convergence,

-

supports all code rates, 1/2, 5/8, 3/4, and 13/16,

- has configurable max-iterations input,

- and implements early termination to save energy.

Depending on your requirement, the IP-core deliverable may include:

- System Verilog source code,

- System Verilog testbench,

- Synthesized netlist,

- Matlab or C bit-accurate model for simulation.

Test-implementation results:

-

Node: 40nm CMOS,

-

Peak Throughput: 8.4 Gbps,

-

Clock Frequency: 200 MHz,

-

Core Area: 1.44 mm2.