XCEL ASICs

GmbH

Accelerator IP for 5G-NR Polar Decoder

Polar codes are capacity-approaching codes for the small block lengths, and therefore, are chosen for the 5G-NR control channels. This IP core implements an optimized Polar decoder that is compliant with 5G-NR Polar decoding, 3GPP release 15.

The IP core:

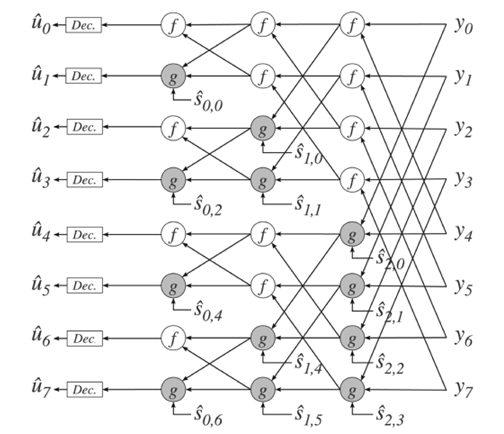

- implements simplified successive cancellation decoding,

- supports code lengths of up to 512 bits,

- significantly improves latency and throughput of the decoder by implementing radix-n F and G accelerators.

Depending on your requirement, the IP-core deliverable may include:

-

System Verilog source code,

-

System Verilog testbench,

-

Synthesized netlist,

-

Matlab or C bit-accurate model for simulation.

Test-implementation results:

-

Node: 65nm CMOS,

-

Peak Throughput: 1 Gbps,

-

Clock Frequency: 300 MHz,

-

Core Area: 0.35 mm2.