XCEL ASICs

GmbH

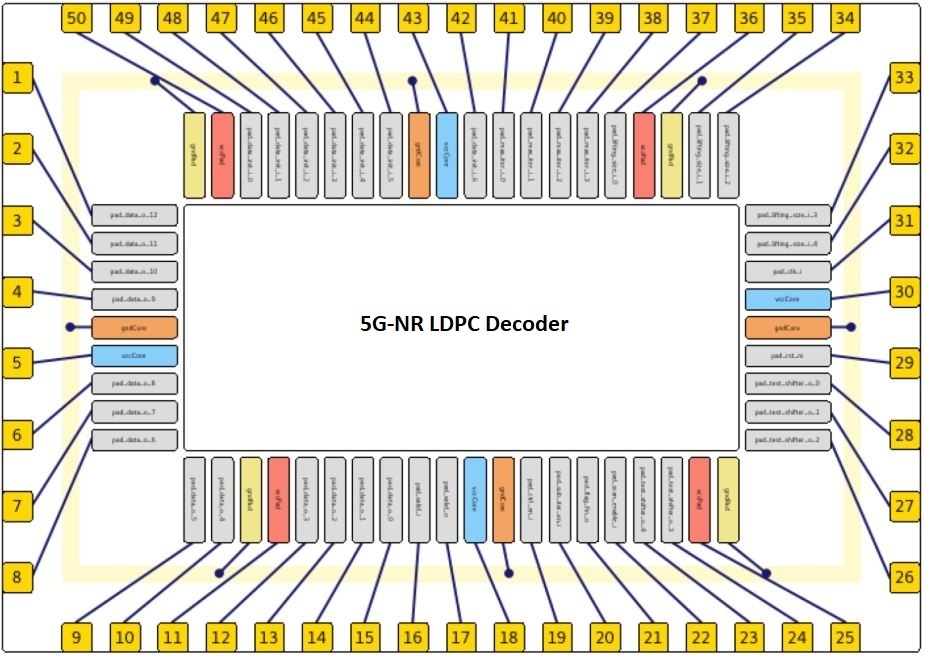

Accelerator IP for 5G-NR LDPC Decoder

This silicon IP core implements an optimized low-density parity-check (LDPC) decoder compliant with the 5G New Radio (5G-NR) standard as defined in 3GPP Release 15. Designed for integration into 5G transceiver chips, the IP core meets the stringent demands of modern wireless communication systems for high throughput, low latency, and silicon and energy efficiency. A cross-layer optimization of algorithm, architecture, and circuit provides one the best-reported power, performance, and area results for a 5G-NR LDPC decoder. Key features of the IP core are:

-

implements layered LDPC decoding for faster convergence,

-

supports all code rates for base graph 1,

-

supports all code rates for base graph 2,

- has configurable max-iterations input,

- and implements early termination to save energy.

Depending on your requirement, the IP-core deliverable may include:

- System Verilog source code,

- System Verilog testbench,

- Synthesized netlist,

- Matlab or C bit-accurate model for simulation.

Test-implementation results:

-

Node: 65nm CMOS,

-

Peak Throughput: 7.1 Gbps,

-

Clock Frequency: 150 MHz,

-

Core Area: 4 mm2.