XCEL ASICs

GmbH

Accelerator IP for WiFi

(IEEE 802.11 n/ac/ax/be) LDPC Decoder

This optimized silicon IP core is designed for IEEE 802.11 n/ac/ax/be (WiFi 4/5/6/7) compliant low-density parity-check (LDPC) decoding and addresses the growing demand for high-throughput solutions in WiFi transceiver chips — with a minimal area footprint. The IP core can meet the stringent 30 Gbps throughput requirements of the latest WiFi 7 (IEEE 802.11be) standard. A cross-layer optimization of algorithm, architecture, and circuit has resulted in the best-reported power, performance, and area results for a WiFi-compliant LDPC decoder. Key features of the IP are:

-

implements layered LDPC decoding for faster convergence,

-

supports all code rates: 1/2, 2/3, 3/4, 5/6,

-

supports all frame lengths: 648, 1296, 1944,

- has configurable max-iterations input,

- and implements early termination to save energy.

Depending on your requirement, the IP-core deliverable may include:

- System Verilog source code,

- System Verilog testbench,

- Synthesized netlist,

- Matlab or C bit-accurate model for simulation.

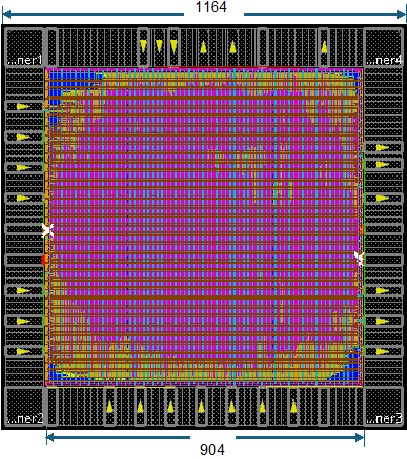

Test-implementation results:

-

Node: 28nm CMOS,

-

Peak Throughput: 24.3 Gbps,

-

Clock Frequency: 400 MHz,

-

Core Area: 904x904=0.82 mm2.