XCEL ASICs

GmbH

We accelerate your ASIC or FPGA development

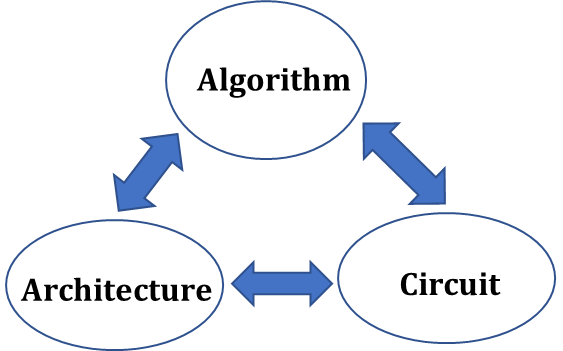

XCEL ASICs is a deep-tech startup specializing in optimized silicon IP cores and design services. We design, simulate, implement, and verify high-performance digital systems targeting ASIC and FPGA platforms, with a focus on advanced wireless communication and machine learning applications. At XCEL ASICs, we leverage a cross-layer approach — algorithm, architecture, and circuit co-design — to optimize performance, power, and area in silicon implementations.

Our portfolio includes state-of-the-art accelerator IP cores for communication or memory systems. Some of our recent innovations include:

-

An ultra-high-throughput WiFi LDPC decoder — designed to meet next-gen connectivity demands,

-

An area-efficient high-throughput LDPC decoder for 5G-NR with full standard compliance,

-

A multi-Gbps LDPC decoder for WiGig (60 GHz) wireless systems,

-

An optimized 5G-NR polar decoder, engineered for performance and low latency.

Cross-Layer Optimization

XCEL ASICs is an official member of the Altera Solution Acceleration Partner (ASAP) program, enabling deeper collaboration and access to advanced FPGA platforms to accelerate innovation at scale.

Services:

-

ASIC development and FPGA prototyping for communication, AI, and DSP applications,

-

Simulation and verification of ASICs and standalone IP cores,

-

Synthesis, placement, and routing of digital blocks for ASIC tapeout,

-

Design, simulation, and implementation of digital communication, AI, or DSP systems.